计算机组成与设计笔记

计算机系统概述

计算机系统由硬件(Hardware)和软件(Software)两大部分组成,二者协同工作实现计算功能。

硬件是计算机的物理实体部分,基于电子学、光学和机械原理实现,主要包括:

- 核心部件:CPU(运算器+控制器)、存储器(内存/外存)、输入/输出设备

- 基础架构:总线系统、电源模块、主板、接口电路等

- 扩展设备:GPU、TPU等专用处理器

软件是运行在硬件上的程序和数据集合,可分为多个层次:

- 系统软件:操作系统(进程管理、内存管理、文件系统等)、编译器/解释器(将高级语言转换为机器代码)、设备驱动程序、网络协议栈、系统工具(调试器、链接器等)

- 应用软件:通用应用软件(办公套件、浏览器等)、行业专用软件(CAD、EDA等)、用户定制程序

冯·诺依曼体系架构

冯·诺依曼将计算机架构定义为由运算器、控制器、存储器、输入设备、输出设备五大核心模块组成。现代硬件依然遵循着冯·诺依曼体系结构。

其中运算器(ALU)和控制器封装在CPU中,存储器是主存(RAM)和一些辅助存储(磁盘),输入设备对应鼠标、键盘等设备,输出设备对应显示器等设备。

CPU

cpu 是计算机最核心的组成部分,它由一个芯片及数十亿个晶体管组成,它之于计算机相当于大脑之于人类的关系。

逻辑上可以将 CPU 分为控制单元(CU)及逻辑计算单元(ALU)两部分:

- 控制单元:从内存中提取指令并解码执行。

- 逻辑计算单元:处理算数和逻辑运算。

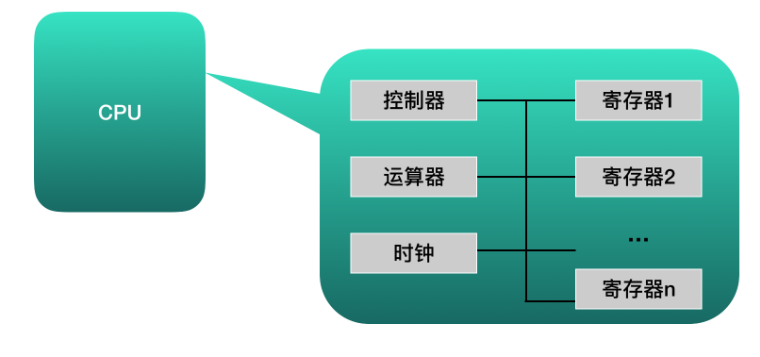

从功能上又可以将 CPU 分为控制器、运算器、时钟、寄存器四部分。

- 控制器:负责从内存中提出指令/数据到寄存器,并根据指令结果控制计算机。

- 运算器:对寄存器内的数据进行运算

- 时钟:负责向cpu发送开始记时的信号。

- 寄存器:cpu的重要组成部分,负责临时存储地址/数据/指令,类似于内存的作用,一个cpu中有20-100个不同种类的寄存器。

程序运行时,程序计数器存储的是程序第一条指令的地址,控制器根据该地址从内存中取出指令分析并执行(顺序执行/条件分支/循环执行),并且将程序计数器修改为下一条指令的地址。

存储器

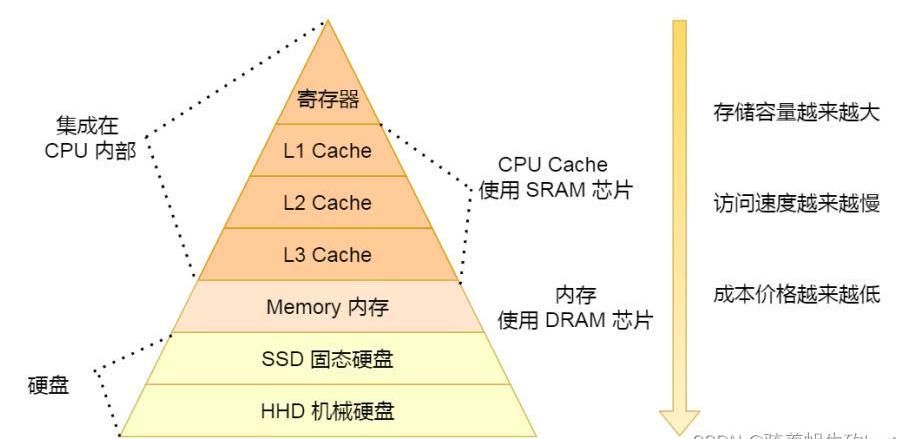

存储器有多种类型,如果根据数据是否易失的,可以分为内存和硬盘两种。 内存的访问速度很快,但是空间有限,并且断电后数据就会消失。 硬盘存储空间充足,并且支持数据持久化存储,但是访问速度较慢。硬盘主要用来解决内存存储空间有限和数据易失的问题。

内存的读写速度已经很快了,但是与CPU相比,仍然相形见绌,CPU需要对内存执行读取命令、数据,回写数据等操作,由于运行速度上的差异,CPU大部分时间都在等待内存响应。 为了减少由于速度差异导致的CPU利用效率问题,现代计算机硬件系统采用多级缓存策略,直接将高速缓存模块(L1)集成在CPU上,CPU可以提前将内存中的数据加载至高速缓存中, 由于高速缓存距离CPU更近以及材质升级等原因,对高速缓存的访问速度有更大的提升。但是高速缓存的内存容量非常有限(内存速度越快,价格越贵,空间也越小),只能缓存少量数据。 因此又在主板上集成了L2缓存。L2缓存相比与L1缓存有更大的内存空间,由于其直接集成在主板上,与CPU也有专用的线路,所有访问速度同样比主存快上很多倍。

总线

计算机几乎所有的交互都需要CPU的参与,CPU与存储器、输入设备和输出设备之间通过总线进行数据传输。总线系统也有多种模式。

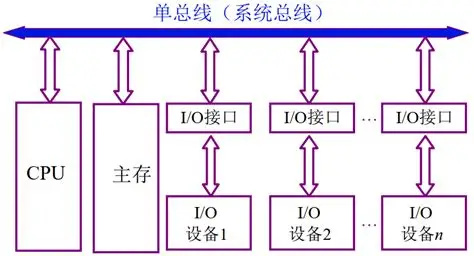

单总线模式

结构如下图所示:cpu与其他设备间的传输通过总线进行传递。在同一时间点,总线只能处理cpu与一个设备间的数据传输,当存在多条数据传输请求时,可能会根据设备的优先级进行选择。总线中也包括控制总线和数据总线,控制总线用来处理控制信息,比如设备需要先通过控制总线请求,获得允许后,才能正式传输数据。

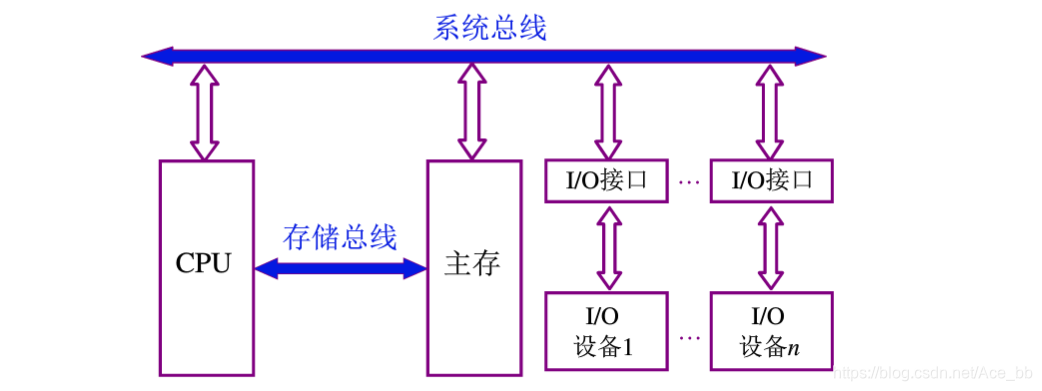

双总线模式

双总线模式在CPU与主存间,增加了一条线路,这样的设计提高了CPU与主存间的数据传输效率。

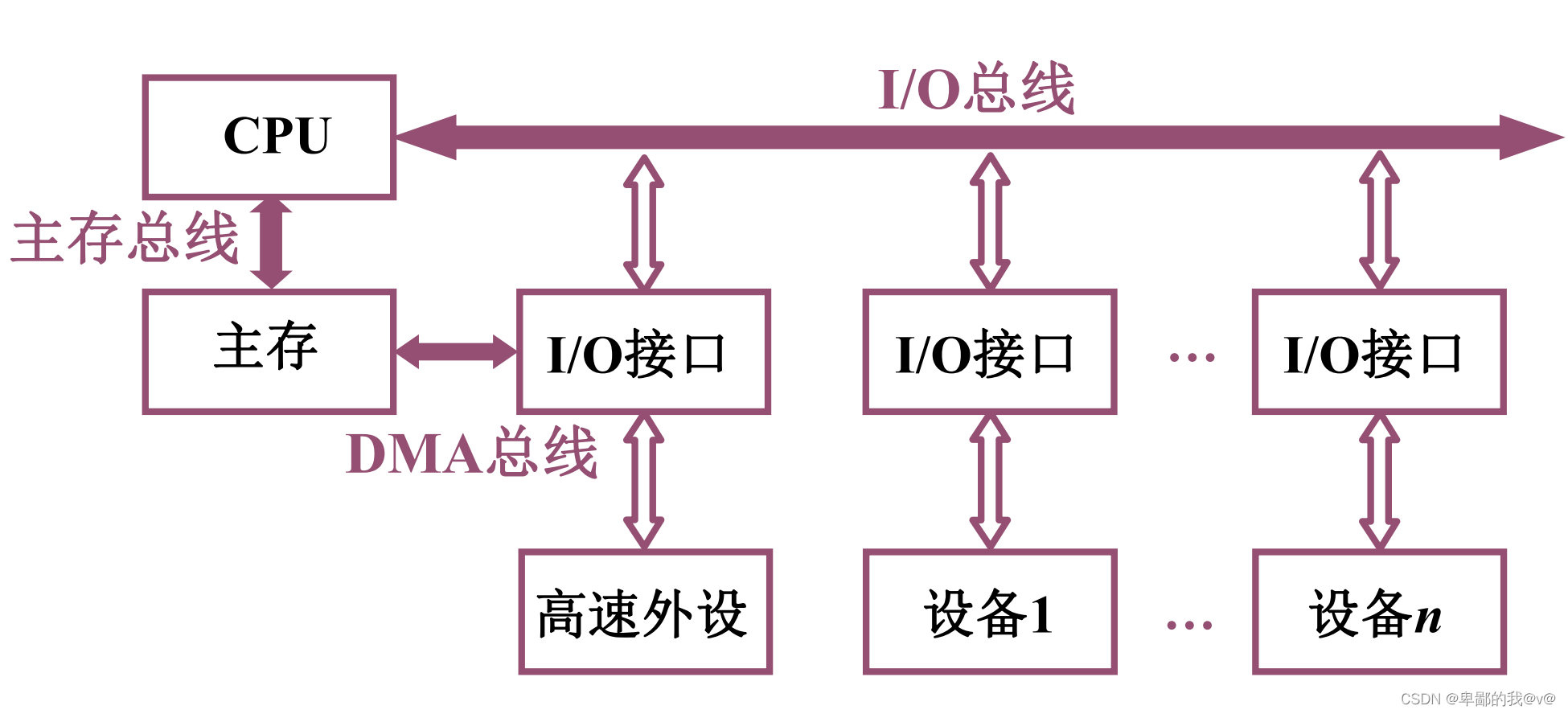

DMA总线模式

在内存与磁盘之间架设了一条DMA(直接内存访问)总线,用来优化加载磁盘数据到内存时,CPU利用率的问题。

传统中断驱动模式(PIO模式)

- CPU向磁盘控制器发出读取指令,指定需要访问的磁盘位置和数据长度

- 磁盘控制器开始机械寻址(磁头移动+盘片旋转),此时CPU可继续执行其他任务

- 当数据准备就绪后,磁盘控制器向CPU发起硬件中断请求

- CPU暂停当前工作,执行上下文切换保存状态,然后处理中断:

- 通过I/O指令将数据从磁盘控制器缓冲区逐字(或逐块)读入内存

- 校验数据完整性

- 中断处理完成后恢复之前任务,产生两次上下文切换开销

DMA(直接内存访问)模式

- CPU初始化DMA控制器:

- 设置目标内存地址

- 指定传输数据量

- 配置磁盘起始位置

- DMA控制器接管总线,直接与磁盘控制器协调数据传输

- 磁盘完成寻址后,数据通过系统总线直接传输到指定内存区域(无需CPU介入)

- 传输完成后DMA控制器发送中断通知CPU进行结果校验